|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SITE MAP |

| NEWS |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Распайка разъема IDE HDD |

RAM |

Распайка Compact Flash |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Распайка шины ISA |

PC/104 |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

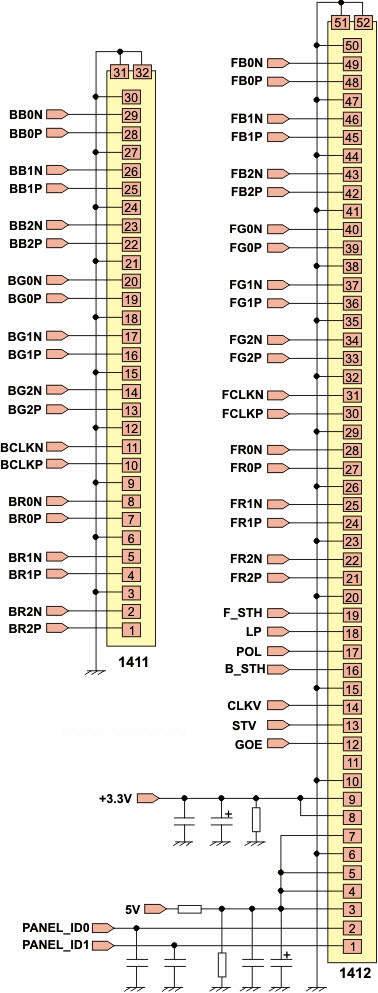

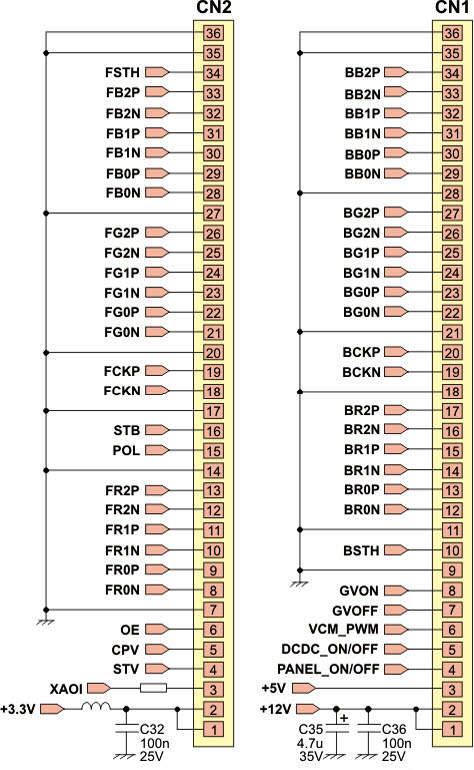

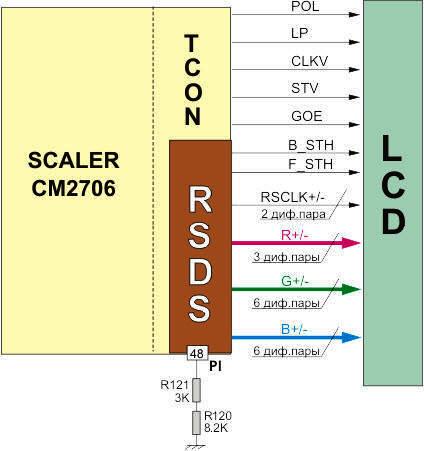

LVDS |

Распайка шины PCI |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Распайка разъема IDE HDD

|

Распайка Compact Flash

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Распайка шины ISA

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Второй вариант |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

ISA=Industry Standard Architecture

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

PC/104 is a compact version of the ISA bus, optimized for the requirements of embedded systems

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Распайка шины PCI

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Шина PCIPCI (англ. Peripheral component interconnect, дословно — взаимосвязь периферийных компонентов) — шина ввода/вывода для подключения периферийных устройств к материнской плате компьютера. Стала массово применяться для Pentium-систем, но используется и с 486 процессорами. Частота шины от 20 до 33 МГц, теоретически максимальная скорость 132/264 Мбайт/с для 32/64 бит. Слот PCI самодостаточен для подключения любого контроллера (VLB не работала без ISA), на системной плате может сосуществовать с любой из других шин ввода-вывода. Шина PCI - первая шина в архитектуре IBM PC, которая не привязана к этой архитектуре. Она является процессорно-независимой и применяется, например, в компьютерах Macintosh. В отличие от остальных шин, компоненты расположены на левой поверхности плат PCI-адаптеров. По этой причине крайний PCI-слот обычно разделяет использование посадочного места с соседним ISA-слотом (Shared slot). Процессор через так называемые мосты (PCI Bridge) может быть подключен к нескольким каналам PCI, обеспечивая возможность одновременной передачи данных между независимыми каналами PCI (возможно только в спецификации 2.1). Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 восьмибитных регистров, не приписанных ни к пространству памяти, ни к пространству ввода-вывода. Доступ к ним осуществляется по специальным циклам шины Configuration Read и Configuration Write, вырабатываемым контроллером при обращении процессора к регистрам контроллера шины PCI, расположенным в его пространстве ввода-вывода. На PCI определены два основных вида устройств - инициатор (по ГОСТ - задатчик), т.е. устройство, получившее от арбитра шины разрешение на захват ее и устройство назначения, цель (target) с которым инициатор выполняет цикл обмена данными.

- PCI 2.0 — первая версия базового стандарта, получившая широкое распространение, использовались как карты, так и слоты с сигнальным напряжением только 5 В. Пиковая пропускная способность — 133 Мбайт/с; - PCI 2.1-3.0 — отличались от 2.0 возможностью одновременной работы нескольких bus-master устройств (т. н. конкурентный режим), а также появлением универсальных карт расширения, способных работать как в 5 В, так и в 3,3 В слотах (с частотой 33 и 66 МГц соответственно). Пиковая пропускная способность для 33 МГц — 133 Мбайт/с, а для 66 МГц — 266 Мбайт/с; Версия 2.1 — работа с 3,3 В картами и наличие соответствующих линий питания являлась опциональной; Версия 2.2 — сделанные в соответствии с этими стандартами карты расширения имеют универсальный разъём и способны работать практически во всех более поздних разновидностях слотов шины PCI, а также, в некоторых случаях, и в слотах 2.1; Версия 2.3 — несовместима с картами PCI 5 В, несмотря на продолжающееся использование 32-битных слотов с 5 В-ключом. Карты расширения имеют универсальный разъём, но не способны работать в 5 В-слотах ранних версий (до 2.1 включительно); Версия 3.0 — завершает переход на карты PCI 3,3 В, карты PCI 5 В больше не поддерживаются. - PCI 64 — расширение базового стандарта PCI, появившееся в версии 2.1, удваивающее число линий данных, и, следовательно, пропускную способность. Слот PCI64 является удлинённой версией обычного PCI-слота. Формально совместимость 32-битных карт с 64-битным слотами (при условии наличия общего поддерживаемого сигнального напряжения) полная, а совместимость 64-битной карты с 32-битным слотами является ограниченной (в любом случае произойдёт потеря производительности). Работает на тактовой частоте 33 МГц. Пиковая пропускная способность — 266 Мбайт/с; Версия 1 — использует слот PCI 64-бита 5 В; Версия 2 — использует слот PCI 64-бита 3,3 В; - PCI 66 — это PCI 64 работающий на тактовой частоте 66 МГц, использует 3,3 В-слоты, карты имеют универсальный, либо 3,3 В форм-фактор. Пиковая пропускная способность — 533 Мбайт/с; - PCI 64/66 — комбинация PCI 64 и PCI 66, позволяет учетверить скорость передачи данных по сравнению с базовым стандартом PCI, и использует 64-битные 3,3 В-слоты, совместимые только с универсальными и 3,3 В 32-битными картами расширения. Карты стандарта PCI64/66 имеют универсальный (имеющий ограниченную совместимость с 32-битными слотами) либо 3,3 В форм-фактор (последний вариант принципиально не совместим с 32-битными 33 МГц слотами популярных стандартов). Пиковая пропускная способность — 533 Мбайт/с; - PCI-X — расширение PCI64, для всех вариантов шины существуют следующие ограничения по количеству подключаемых к каждой шине устройств: 66 МГц — 4, 100 МГц — 2, 133 МГц — 1 (или 2, если одно или оба устройства не находятся на платах расширения, а уже интегрированы на одну плату вместе с контроллером), 266, 533 МГц и выше — 1; Версия 1.0 — введено две новые рабочие частоты: 100 и 133 МГц, а также механизм раздельных транзакций для улучшения производительности при одновременной работе нескольких устройств. Как правило, обратно совместима со всеми 3,3 В и универсальными PCI-картами. Карты обычно выполняются в 64-битном 3,3 В формате и имеют ограниченную обратную совместимость со слотами PCI64/66, а некоторые — в универсальном формате и способны работать (хотя практической ценности это почти не имеет) в обычном PCI 2.2/2.3. Пиковая пропускная способность — 1024 Мбайт/с; Версия 2.0 — введено две новые рабочие частоты: 266 и 533 МГц, а также коррекция ошибок чётности при передаче данных (ECC). Расширяет конфигурационное пространство PCI до 4096 байт и допускает расщепление на 4 независимых 16-битных шины, что применяется исключительно во встраиваемых и промышленных системах, сигнальное напряжение снижено до 1,5 В, но сохранена обратная совместимость разъёмов со всеми картами, использующими сигнальное напряжение 3,3 В. Пиковая пропускная способность — 4096 Мбайт/с; - Mini PCI — новый форм-фактор PCI 2.2 для использования в основном в ноутбуках; - Cardbus — PCMCIA форм-фактор для 32-бит, 33 МГц PCI; - CompactPCI — использует модули размера Eurocard, включаемые в PCI backplane; - PC/104-Plus — индустриальная шина, использующая сигнализацию PCI с другим разъёмом; - PMC — PCI mezzanine card, мезонинная шина, соответствует стандарту IEEE P1386.1; - ATCA или AdvancedTCA — шина следующего поколения для телекоммуникационной индустрии. Cводная таблица совместимости карт и слотов в зависимости от версии и конструктива:

сначала была шина ISA (давным-давно) со временем она стала узким местом

для многих устройств и на смену ей пришла шина PCI когда и ее стало

маловато решили частично снять вопрос создав специализированную

графическую шину AGP (чем то напоминает историю с VLB - Vesa Local Bus

во времена ISA - была у меня такая длинная видеокарта и память туда

можно было вставлять увеличивая объем с 512Кб до 2Мб Peripheral component interconnect, дословно: взаимосвязь периферийных компонентов) — системная шина для подключения периферийных устройств к материнской плате компьютера. * частота шины — 33,33 МГц или 66,66 МГц, передача синхронная; * разрядность шины — 32 или 64 бита, шина мультиплексированная (адрес и данные передаются по одним и тем же линиям); * пиковая пропускная способность для 32-разрядного варианта, работающего на частоте 33,33 МГц — 133 Мб в секунду; * адресное пространство памяти — 32 бита (4 Гибибайта); * адресное пространство портов ввода-вывода — 32 бита (4 Гибибайта); * конфигурационное адресное пространство (для одной функции) 256 байт; * напряжение 3,3 или 5 вольт. # PCI 2.0 — первая версия базового стандарта, получившая широкое распространение, использовались как карты, так и слоты с сигнальным напряжением только 5В. Пиковая пропускная способность — 133Мб/с; # PCI 2.1-3.0 — отличались от 2.0 возможностью одновременной работы нескольких bus-master устройств (т. н. конкурентный режим), а также появлением универсальных карт расширения, способных работать как в 5В, так и в 3.3В слотах (с частотой 33 и 66 МГц соответственно). Пиковая пропускная способность для 33 МГц — 133МБ/с, а для 66 МГц — 266 МБ/с; * Версия 2.1 — работа с 3.3В картами и наличие соответствующих линий питания являлась опциональной; * Версия 2.2 — сделанные в соответствии с этими стандартами карты расширения имеют универсальный разъём и способны работать практически во всех более поздних разновидностях слотов шины PCI, а также, в некоторых случаях, и в слотах 2.1; * Версия 2.3 — несовместима с картами PCI 5В, несмотря на продолжающееся использование 32-битных слотов с 5В-ключом. Карты расширения имеют универсальный разъём, но не способны работать в 5В-слотах ранних версий (до 2.1 включительно); * Версия 3.0 — завершает переход на карты PCI 3.3В, карты PCI 5В больше не поддерживаются. # PCI 64 — расширение базового стандарта PCI, появившееся в версии 2.1, удваивающее число линий данных, и, следовательно, пропускную способность. Cлот PCI64 является удлинённой версией обычного PCI-слота. Формально совместимость 32-битных карт с 64-битным слотами (при условии наличия общего поддерживаемого сигнального напряжения) полная, а совместимость 64-битной карты с 32-битным слотами является ограниченной (в любом случае произойдёт потеря производительности). Работает на тактовой частоте 33МГц. Пиковая пропускная способность — 266 МБ/с; * Версия 1 — использует слот PCI 64-бита 5В; * Версия 2 — использует слот PCI 64-бита 3.3В; # PCI 66 — это PCI 64 работающий на тактовой частоте 66 МГц , использует 3.3В-слоты, карты имеют универсальный, либо 3.3В форм-фактор. Пиковая пропускная способность — 533 МБ/с; # PCI 64/66 — комбинация PCI 64 и PCI 66, позволяет учетверить скорость передачи данных по сравнению с базовым стандартом PCI, и использует 64-битные 3.3В слоты, совместимые только с универсальными и 3.3В 32-битными картами расширения. Карты стандарта PCI64/66 имеют универсальный (имеющий ограниченную совместимость с 32-битными слотами) либо 3.3В форм-фактор (последний вариант принципиально не совместим с 32-битными 33МГц слотами популярных стандартов). Пиковая пропускная способность — 533 МБ/с; # PCI-X — расширение PCI64, для всех вариантов шины существуют следующие ограничения по количеству подключаемых к каждой шине устройств: 66МГц — 4, 100МГц — 2, 133МГц — 1 (или 2 если одно или оба устройства не находятся на платах расширения, а уже интегрированы на одну плату вместе с контроллером), 266, 533МГц и выше — 1; * Версия 1.0 — введено две новые рабочие частоты: 100 и 133МГц, а также механизм раздельных транзакций для улучшения производительности при одновременной работе нескольких устройств. Как правило, обратно совместима со всеми 3.3В и универсальными PCI-картами. Карты обычно выполняются в 64-битном 3.3В формате и имеют ограниченную обратную совместимость со слотами PCI64/66, а некоторые — в универсальном формате и способны работать (хотя практической ценности это почти не имеет) в обычном PCI 2.2/2.3. Пиковая пропускная способность — 1024 МБ/с; * Версия 2.0 — введено две новые рабочие частоты: 266 и 533МГц, а также коррекция ошибок чётности при передаче данных (ECC). Расширяет конфигурационное пространство PCI до 4096 байт и допускает расщепление на 4 независимых 16-битных шины, что применяется исключительно во встраиваемых и промышленных системах, сигнальное напряжение снижено до 1.5В, но сохранена обратная совместимость разъёмов со всеми картами, использующими сигнальное напряжение 3.3В. Пиковая пропускная способность — 4096 МБ/с;

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

PCI Express или PCIe или PCI-E,

(также известная как 3GIO for 3rd Generation I/O; не путать с PCI-X или

PXI) — компьютерная шина, использующая программную модель шины PCI и

высокопроизводительный физический протокол, основанный на

последовательной передаче данных. |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Распайка кабеля Cisco Console RJ45 - DB9RJ45 DB9 RTS 1 8 CTS DTR 2 6 DSR TXD 3 2 RXD GND 4 5 GND GND 5 5 GND RXD 6 3 TXD DSR 7 4 DTR CTS 8 7 RTS

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Свойства интегрированных устройствКак правило, в материнскую плату встроен ряд контроллеров периферийных устройств: контроллер IDE, контроллер последовательных и параллельных портов, клавиатуры, флоппи-дисковода и пр. Иногда возникает необходимость отключения некоторых устройств - например, для отладки или освобождения прерываний. В разделе INTEGRATED PERIPHERALS обычно можно встретить следующие пункты:

PIO Скорость, Мб/с 0 3,3 1 5,2 2 8,3 3 11,6 4 16,6

Свойства слотов PCIО функциях этого раздела обычно вспоминают тогда, когда возникают конфликты по прерываниям между устройствами ISA и PCI. Дело в том, что одной из задач BIOS при загрузке компьютера является правильное распределение системных ресурсов. Согласно этой технологии карта PCI может быть настроена на работу с определенным прерыванием и с определенным портом ввода-вывода. Больше того: одно и то же прерывание может совместно использоваться несколькими устройствами PCI. Информация о распределении ресурсов хранится в специальной таблице - ESCD (Extended System Configuration Data). Но это еще не все. ОС, поддерживающая PnP, позже может перераспределить ресурсы по своему усмотрению. Считается, что Windows справляется с этой задачей эффективнее, чем BIOS компьютера. Однако идиллию портят карты ISA, не поддерживающие PnP. Они настраиваются с помощью перемычек или специальных утилит. Поэтому может возникнуть необходимость закрепить за ISA-слотом определенное прерывание. Для этой цели служат следующие параметры:

Управление питаниемСовременные BIOS позволяют оперировать четырьмя состояниями энергопотребления компьютера: работа на "полных оборотах", режим сниженной частоты центрального процессора (Doze), режим ожидания Standby (обычно заключающийся в отключении видео и жестких дисков), "спящий" режим Suspend (максимально низкое энергопотребление, отключение устройств). Система контролируется с помощью счетчика простоя определенных устройств. Если эти устройства бездействуют в течение определенного времени, система переходит в то или иное состояние пониженного энергопотребления. В начале раздела BIOS, управляющего режимами питания, пользователю предлагается выбрать схемы энергосбережения: две стандартные (Min saving и Max Saving) и настраиваемую. Возможно, вам подойдет одна из готовых схем. В противном случае выберите режим User define и введите вручную следующие уточняющие значения:

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

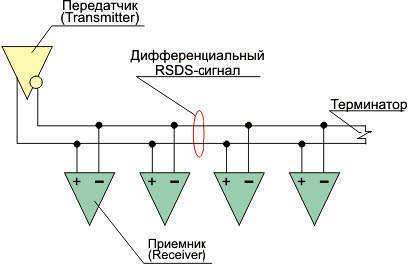

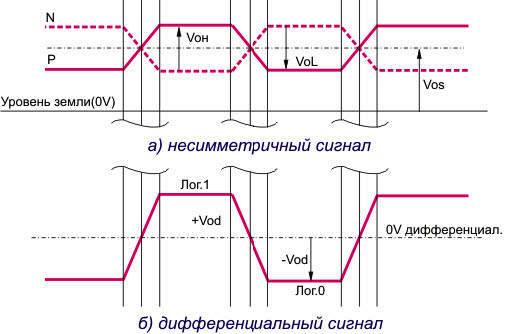

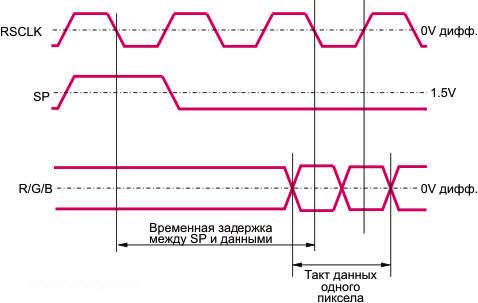

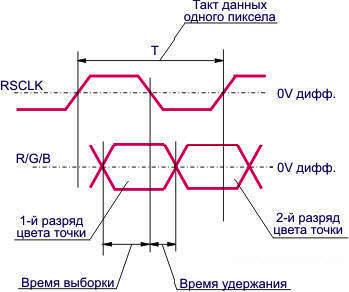

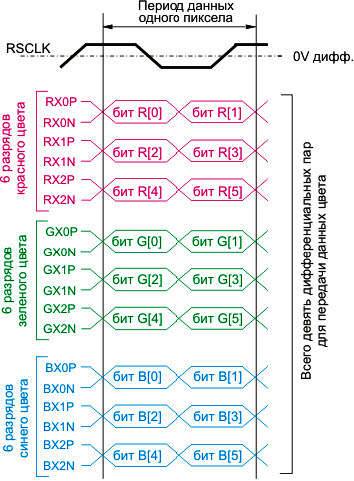

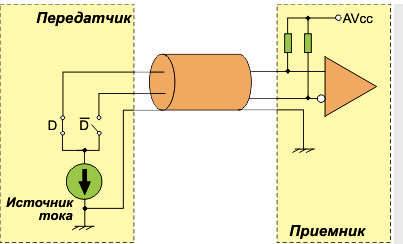

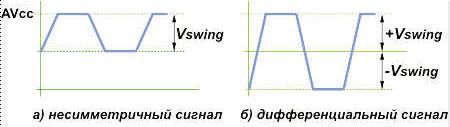

LVDS Материал из Википедии — свободной энциклопедии Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющийпередавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компаниейTexas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин. Стандартизовано как ANSI/TIA/EIA-644-A в 2001 году. Отличия от несимметричной передачи сигналов При низковольтной дифференциальной передаче для передачи одного сигнала используется дифференциальная пара (сигналов); это означает, что передающая сторона подаёт на проводники пары различные уровни напряжения, которые сравниваются на приёмной стороне: для декодирования информации используется разница напряжений на проводниках пары. Передатчик направляет небольшой ток (порядка 3,5 мА) в один из сигнальных проводников, в зависимости от того, какой логический уровень надо передать. На приёмной стороне ток проходит через резистор сопротивлением 100—120 Ом (равным волновому сопротивлению кабеля для уменьшения отраженного сигнала) и возвращается к отправителю сигнала по другому проводнику, образуя таким образом замкнутую электрическую цепь. В соответствии с законом Ома напряжение на резисторе будет составлять около 350 мВ. Принимающая сторона определяет полярность этого напряжения для того, чтобы определить логический уровень. Такой тип передачи называется токовая петля. Небольшая амплитуда сигнала, а также высокая электромагнитная связь проводов пары друг с другом позволяют уменьшить излучаемые вовне помехи и рассеиваемую мощность. Синфазное напряжение (среднее напряжение двух проводников) обычно составляет около 1,25 В, что позволяет использовать LVDS во многих СБИС с напряжением питания 2,5 В и ниже. Как упоминалось выше, напряжение между проводниками пары составляет 350 мВ, что позволяет по сравнению с другими способами передачи сигналов значительно снизить потребляемую мощность. Например, статическая мощность, рассеиваемая на нагрузочном резисторе LVDS, составляет всего 1,2 мВт, по сравнению с 90 мВт, рассеиваемыми на нагрузочном резисторе интерфейса RS-422. Без нагрузочного резистора для каждого бита данных приходилось бы нагружать и разгружать весь проводник. Использование нагрузочного резистора и высоких частот передачи приводит к тому, что бит покрывает лишь часть проводника (в процессе передачи со скоростью электромагнитных колебаний в среде), что является более энергоэффективным. LVDS — не единственная используемая дифференциальная система. Но она остается единственной, сочетающей в себе высокие скорости и небольшое рассеивание энергии. Применение LVDS LVDS стала популярна в конце 90-х годов XX века. До того времени компьютеры были слишком медленны, чтобы требовать столь высоких скоростей передачи данных, используя для передачи данных большое количество проводников (см. напр. ATA). Однако, расширение использования мультимедиа и суперкомпьютеров привело к проявлению широкого интереса к данной системе, так как подобные системы нуждались в передаче больших объёмов данных на расстояния порядка нескольких метров. LVDS используется в таких компьютерных шинах как HyperTransport, FireWire, USB 3.0, PCI Express, DVI, Serial ATA, SAS и RapidIO. Также поддерживается в SCSI, начиная с версии Ultra-2 SCSI для увеличения допустимых длин проводов и скоростей. Современные ПЛИС (например, от Altera или Xilinx) имеют LVDS-порты, что позволяет разрабатывать любые устройства, работающие с шиной на основе LVDS-технологии. Сравнение с параллельной передачей данных LVDS применяется как при параллельной, так и при последовательной передаче данных. При обычной параллельной передаче несколько бит передаются одновременно по группе проводов с использованием общей земли. Высокие скорости LVDS и использование самосинхронизирующихся кодов позволяют передавать больше данных по меньшему количеству проводов, чем в случае параллельной шины. Устройство преобразования между последовательными и параллельными шинами называется сериализатор/десериализатор (сериалайзер/десериалайзер) (англ. serializer/deserializer, SerDes). Многоточечный LVDS Когда скорости последовательной передачи не хватает, данные могут передаваться параллельно по нескольким парам LVDS для каждого бита или байта (например, как в PCI Express или в HyperTransport). Такая система называется шиной LVDS (англ. bus LVDS, BLVDS). Стандартные передатчики рассчитаны на использование в соединениях точка-точка, но для использования в многоточечных шинных системах модифицированные передатчики имеют большие выходные токи, которые могут нагружать несколько терминирующих резисторов. Существует стандарты на подобные системы: BLVDS и LVDM (от Texas Instruments). Также существует стандарт TIA-899 Multipoint LVDS (MLVDS), который используется в AdvancedTCA. MLVDS имеет 2 типа приемников: тип 1 практически совместим с LVDS и использует порог в 0 В; тип 2 использует порог в 0,1 В, чтобы избегать различных ошибок, например возникновения незамкнутых и короткозамкнутых цепей.

LCD-мониторы становятся основными устройства воспроизведения информации, а это значит, что их применение носит поистине массовый характер. Все это означает, что в соответствии с законом больших чисел, количество отказов мониторов и их наиболее сложной части - LCD-панелей, происходит все чаще, т.е. все чаще перед специалистами сервисных служб стает вопрос о методах диагностики жидкокристаллических матриц. Одним из первых, в этом случае, диагностируется внешний интерфейс, через который на LCD-матрицу передаются все данные. Именно обзору этих интерфейсов посвящен данный материал.

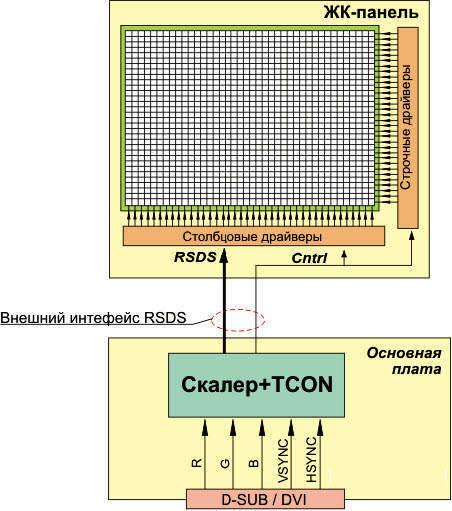

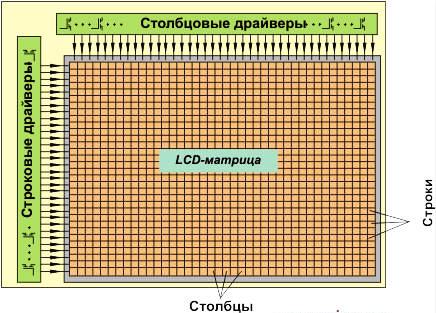

Сейчас уже ни для кого не секрет, что топология абсолютно любого

жидкокристаллического (ЖК) экрана представляет собой матрицу,

образованную системой строковых и столбцовых электродов. При этом каждый

элемент изображения находится на пересечении строки и столбца (рис.1). Рис.1 Каждая ячейка матрицы адресуется номером строки и номером столбца

Для

включения соответствующего пиксела (точки) должен быть выбран столбец и

должна быть указана строка, в которой находится этот пиксел. В

результате, к ЖК-ячейке прикладывается напряжение, величина которого

определяет яркость точки. Выборка строк и столбцов осуществляется

переключением ключевых транзисторов, которые образуют так называемые,

драйверы столбцов (Column Driver-CD или Source Driver-SD) и драйверы

строк (Row Driver-RD или Gate Driver-GD). Естественно, что количество

транзисторов, содержащихся в столбцовых драйверах должно точно

соответствовать количеству столбцов, а количество ключевых транзисторов

строковых драйверов должно равняться количеству строк на экране.

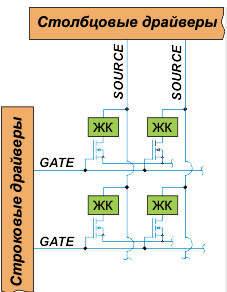

Непосредственную коммутацию ЖК-ячейки осуществляет TFT (тонкопленочный

транзистор). Количество TFT-транзисторов равно количеству ЖК-ячеек.

Напомним, что напряжение, прикладываемое к ЖК-ячейке, формируется

столбцовым драйвером, а драйверы строк формируют сигнал

открывания/запирания TFT-транзистора (рис.2). Рис.2 Эквивалентная схема управления ЖК-ячейками Так, например, в цветной панели 1024х768 точек, имеется 1024 столбца и 768 строк, при этом, так как панель цветная, то и каждый элемент изображения состоит еще из трех элементов – красного, зеленого и синего. Поэтому такая панель содержит 3072 столбца (1024х3) и 768 строк. Таким образом, для управления этой панелью требуется 3072+768=3840 транзисторов. Естественно, что все эти транзисторы размещаются в интегральных микросхемах, образующих вместе с ЖК-панелью единую неразборную конструкцию.

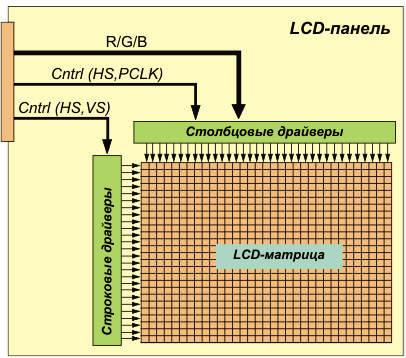

Информация о градации цвета, т.е. о яркости цветной точки передается в

формате R/G/B. Эти данные должны поступать на столбцовые драйверы в

цифровом виде. И уже столбцовыми драйверами эти цифровые данные

преобразуются в аналоговое напряжение, прикладываемое к ЖК-ячейкам.

Строковые драйверы никаких преобразований не выполняют, и поэтому

обеспечивают лишь «перебор» строк, указывая ту строку, ЖК-ячейки которой

засвечиваются в данный момент времени. Таким образом, строковые драйверы

должны получать только лишь управляющие сигналы позволяющие осуществлять

перебор строк. В то же самое время, столбцовые драйверы управляются

сигналами, позволяющими осуществлять перебор точек строки, и

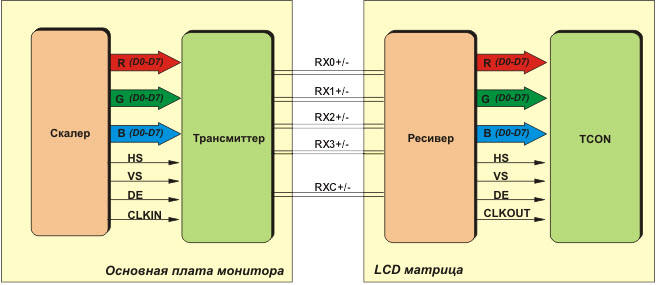

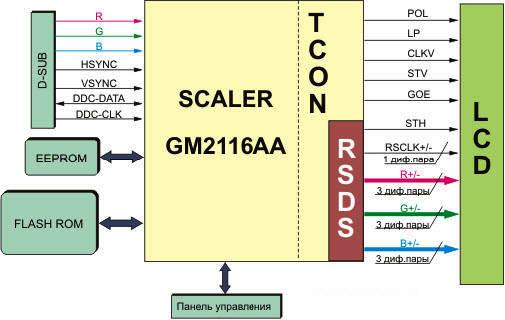

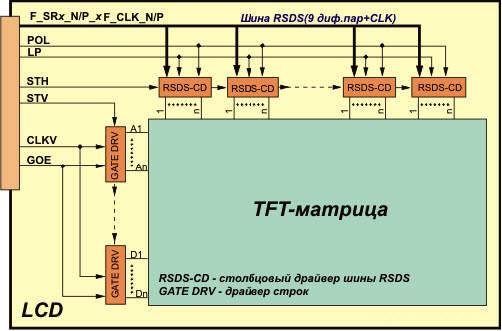

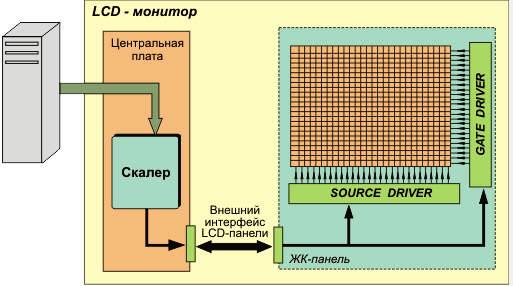

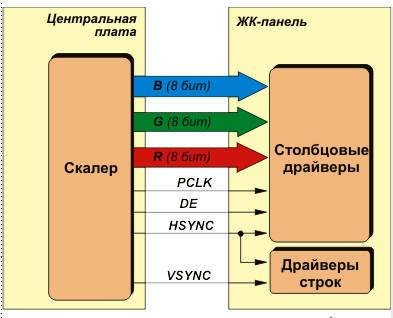

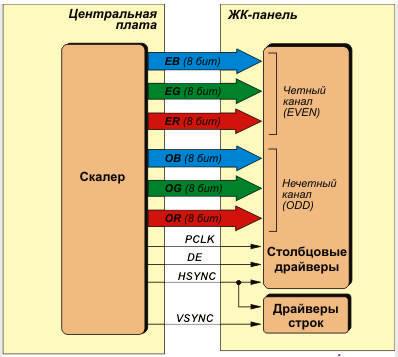

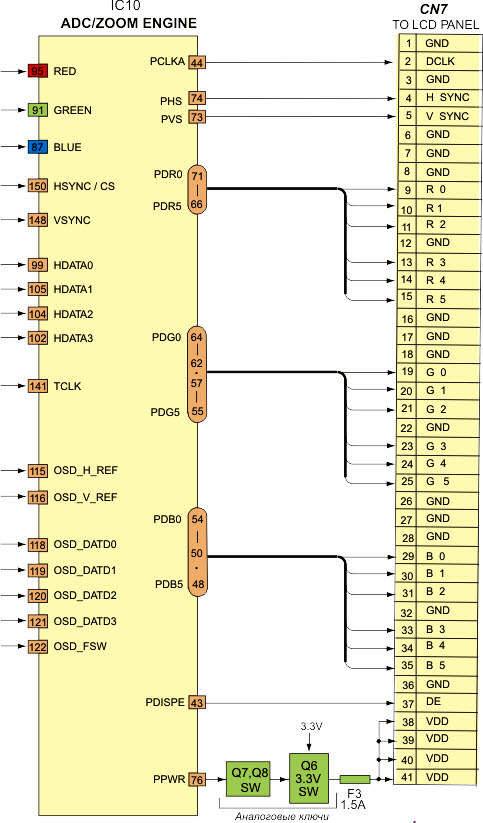

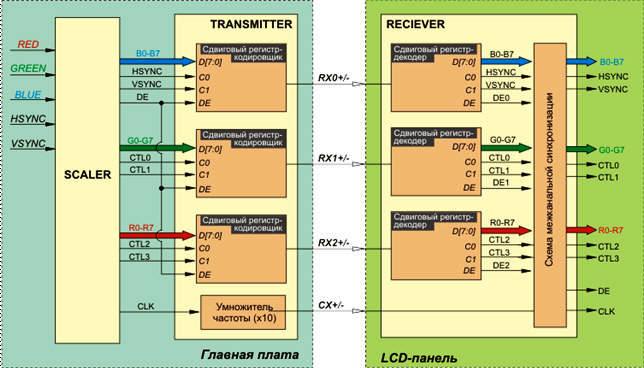

одновременно с этим получают еще и сигналы цвета R/G/B (рис.3). Рис.3 Сигналы, необходимы для управления столбцовыми и строковыми драйверамиСигналы цвета в формате R/G/B, как известно, приходят на вход монитора от персонального компьютера. Эти сигналы обрабатываются графическим контроллером монитора, получившим название скалер (Scaler). Скалер осуществляет преобразование изображения, масштабируя его из любого входного формата в формат, соответствующий разрешению матрицы. Таким образом, данные, передаваемые на LCD-панель, формируются на основной (микропроцессорной) плате монитора, а именно, на выходе микросхемы скалера и передаются на панель с использованием соответствующего интерфейса (рис.4). Этот интерфейс представляет значительный практический интерес для специалиста, осуществляющего диагностику монитора, так как позволяет достаточно точно определить местоположение проблемы – на главной плате монитора или внутри LCD-панели.

Рис.4 Общая архитектура LCD-монитораСуществует несколько способов (несколько интерфейсов) соединения ЖК-панели с главной платой микропроцессора: - параллельный цифровой интерфейс; - интерфейс TMDS; - интерфейс LVDS; - интерфейс RSDS. У производителей LCD-панелей эти интерфейсы пользуются различной популярностью – какие-то интерфейсы безоговорочно доминируют, а применение других является, скорее, экзотикой, чем правилом. Но, тем не менее, с каждым из этих типов интерфейсов встречался любой специалист, имеющий за плечами богатый практический опыт. Поэтому мы и рассмотрим все перечисленные интерфейсы. Параллельный цифровой интерфейс

Это самый первый из внешних

интерфейсов для LCD-панелей. На сегодняшний день он встречается крайне

редко, да и то лишь в устаревших моделях мониторов. У этого типа

соединения много недостатков: Рис.5 При использовании параллельного интерфейса, столбцовые и строковые драйверы напрямую управляются микросхемой скалераПараллельный интерфейс в документации чаще всего обозначают как цифровой интерфейс (Digital), или как TTL интерфейс. И это справедливо, т.к. все сигналы на нем соответствуют TTL-уровням. Наибольшее количество контактов интерфейса соответствует шинам данных цвета. Эти шины, традиционно, бывают двух типов: - 6-разрядные; - 8-разрядные. В первом случае для передачи цвета задействовано 18 цифровых линий (6 бит х 3 цвета), а во втором – 24 цифровых линии (8 бит х 3 цвета). В некоторых случаях можно встретиться с двухканальным исполнением цифрового интерфейса. В данном варианте, цветовые данные могут передаваться либо по 36 линиям (в случае 6-битного кодирования цвета), либо по 48 линиям (в случае 8-битного кодирования цвета) (см. рис.6).

Такое полное отсутствие каких-либо спецификаций на цифровой интерфейс является еще одним отрицательным фактором, определившим отказ разработчиков от его применения. Каждый разработчик LCD-панели использовал цифровой интерфейс с таким количеством контактов и с таким их расположением, которое казалось ему удобным и оптимальным. И зачастую, при появлении новой LCD-панели, тот же самый разработчик мог использовать интерфейс совершенно другой конфигурации. В результате, желание использовать новую модель LCD-панели, приводило к необходимости полностью переделывать главную плату монитора и разводить печатный монтаж заново. Именно поэтому не имеет смысла даже пытаться систематизировать параллельные интерфейсы – все они имеют разное количество контактов, контакты могут располагаться как в один ряд, так и в два ряда, соединительный шлейф может быть как ленточным, так и состоящим из отдельных проводов и т.д. и т.п. Также стоить обратить внимание, что количество и тип управляющих сигналов, таких как сигналы строчной и кадровой синхронизации, тактовой частоты, разрешения и т.п. также не подвергаются спецификации и поэтому наличие всех этих сигналов и их количество является уникальным для каждой модели LCD-панели. Для получения информации о цоколевке внешнего разъема соответствующей LCD-панели, необходимо обратиться к ее документации, благо, что Data Sheet почти на любую модель LCD-панели любого производителя можно найти в Internet'е.

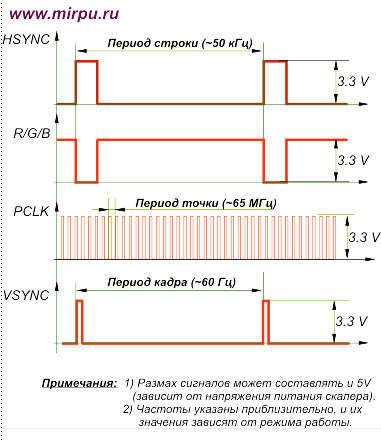

Цифровой интерфейс является очень простым для диагностики. Достаточно

загрузить на экран изображение «белое поле», чтобы добиться активности

абсолютно всех сигналов интерфейса, в чем можно убедиться с помощью

осциллографа. При этом, все активные сигналы будут иметь регулярную

структуру, и их амплитуда будет соответствовать уровням TTL (см. рис.7).

Если же требуется активизировать сигналы какого-то одного цветового

канала, то необходимо загрузить на экран соответствующее «цветовое

поле».

Рис.7 Осциллограмы основных

сигналов параллельного интерфейса при работе монитора с тестовым

изображением "белое поле"

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

№ |

Обознач. |

Сигнал |

|

1 |

GND |

Общий |

|

2 |

VDD |

«Аналоговое» напряжение для пита-ния ЖК и других элементов матрицы |

|

3 |

VDD |

|

|

4 |

VDD |

|

|

5 |

GND |

Общий |

|

6 |

GND |

Общий |

|

7 |

GND |

Общий |

|

8 |

VCC |

Напряжение питания Panel Link |

|

9 |

RX2+ |

«+» дифф. пары №2 (красный цвет) |

|

10 |

RX2- |

«-» дифф. пары №2 (красный цвет) |

|

11 |

VCC |

Напряжение питания Panel Link |

|

12 |

RX1+ |

«+» дифф. пары №1 (зеленый цвет) |

|

13 |

RX1- |

«-» дифф. пары №1 (зеленый цвет) |

|

14 |

VCC |

Напряжение питания Panel Link |

|

15 |

RX0+ |

«+» дифф. пары №0 (синий цвет) |

|

16 |

RX0- |

«-» дифф. пары №0 (синий цвет) |

|

17 |

HSYNC |

Сигнал строчной синхронизации |

|

18 |

RXC+ |

«+» дифф. пары тактовых импульсов |

|

19 |

RXC- |

«-» дифф. пары тактовых импульсов |

|

20 |

VSYNC |

Сигнал кадровой синхронизации |

|

21 |

NC |

Не используется |

В табл.2 представлено описание интерфейса Panel Link монитора LG LB570 (в этой таблице мы намеренно оставили такое же обозначение сигналов, которое используется компанией LG). В этом мониторе LCD-панель также подключается через 21-контактный разъем, но сигналы HSYNC и VSYNC на интерфейсе отсутствуют, т.е. отдельно не передаются. Это означает, что управляющие сигналы, в том числе и HSYNC/VSYNC, передаются в 10-битовом потоке данных по дифференциальным линиям. Сравнение таблиц 1 и 2 показывает, что эти интерфейсы практически идентичны и разнятся они только сигналами HSYNC/VSYNC, да еще буквенным обозначением сигналов.

Таблица 2. Назначение контактов разъема интерфейса Panel Link vонитора LG LB570

|

№ |

Обознач. |

Сигнал |

|

1 |

GND |

Общий |

|

2 |

VDD |

«Аналоговое» напряжение для питания ЖК и других элементов матрицы |

|

3 |

VDD |

|

|

4 |

VDD |

|

|

5 |

GND |

Общий |

|

6 |

GND |

Общий |

|

7 |

TMDSGND |

Общий для TMDS |

|

8 |

TMDSPOWER |

Напряжение питания TMDS |

|

9 |

TMDSREDP |

«+» дифф. пары красного цвета |

|

10 |

TMDSREDN |

«-» дифф. пары красного цвета |

|

11 |

TMDSPOWER |

Напряжение питания TMDS |

|

12 |

TMDSGRNP |

«+» дифф. пары зеленого цвета |

|

13 |

TMDSGRNN |

«-» дифф. пары зеленого цвета |

|

14 |

TMDSPOWER |

Напряжение питания TMDS |

|

15 |

TMDSBLUP |

«+» дифф. пары синего цвета и сигналов HS/VS |

|

16 |

TMDSBLUN |

«-» дифф. пары синего цвета и сигналов HS/VS |

|

17 |

TMDSPOWER |

Напряжение питания TMDS |

|

18 |

TMDSCLKP |

«+» дифф. пары синхроимпульсов |

|

19 |

TMDSCLKN |

«-» дифф. пары синхроимпульсов |

|

20 |

TMDSPOWER |

Напряжение питания TMDS |

|

21 |

NC |

Не используется |

Но еще раз отмечаем, что единого стандарта не существует и это только один из возможных вариантов разъема, хотя и наиболее распространенный. Уточнить тип используемого интерфейса и выяснить распределение сигналов по контактам соединительного разъема, как всегда, можно в Data Sheet'е на LCD-панель.

Но, тем не менее, при использовании TMDS появляется некоторая универсальность соединения LCD-панели с главной платой монитора. Для обеспечения такой унификации, главная плата монитора должна оснащаться универсальным трансмиттером, совместимым с любым ресивером LCD-панели. Кстати сказать, компания Silicon Image является лидером в разработке TMDS трансмиттеров/ресиверов, и их крупнейшим поставщиком, что, в общем-то, и неудивительно. Широкое распространение, в свое время, получили такие пары трансмиттеров/ресиверов, как SIL100/SIL101, SIL150/SIL151, SIL160/SIL161 и др. Если в мониторе используется интерфейс TMDS, то смена LCD-панели не приводит к необходимости переработки всей главной платы – достаточно будет согласовать лишь соединительный шлейф или разъем. В крайнем случае, потребуется замена TMDS-трансмиттера.

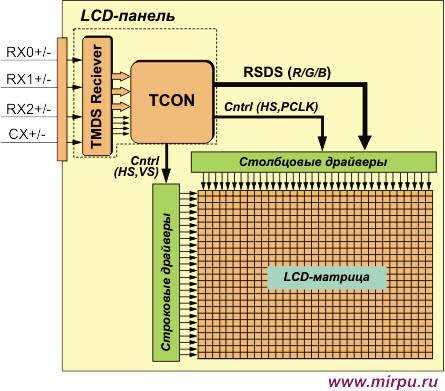

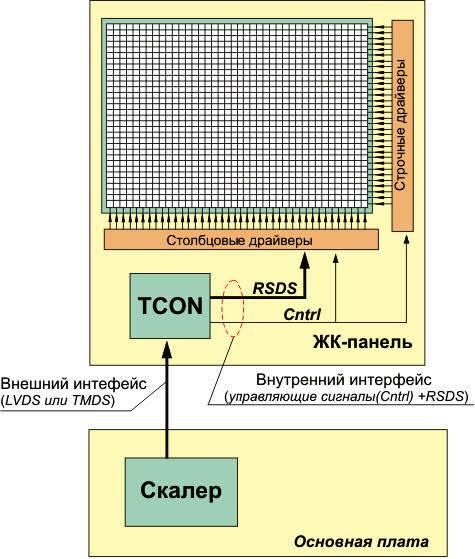

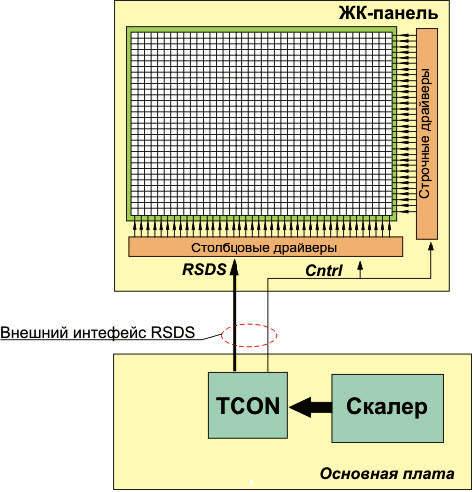

В

случае использования интерфейса TMDS, в составе LCD-панели появляется

специальная микросхема – контроллер синхронизации TCON (Timing

CONtroller). Контроллер TCON осуществляет преобразование входных

сигналов (R/G/B, HSYNC, VSYNC) в сигналы управления столбцовыми и

строковыми драйверами. Внутренняя архитектура LCD-панели при

использовании интерфейса TMDS представлена на рис.17. Необходимо

отметить, что многие контроллеры TCON интегрированы с TMDS-ресивером. В

этом случае входными сигналами TCON являются дифференциальные пары TMDS.Рис.17

Внутренняя архитектура LCD-панели с внешним интерфейсом TMDS

Цветовые данные R/G/B от контроллера TCON к столбцовым драйверам передаются по внутреннему интерфейсу, в качестве которого, чаще всего, используется интерфейс RSDS (реже MLVDS).

Анализ огромного количества LCD-панелей показал, что интерфейс TMDS (Panel Link) использовался и используется крайне редко и его применение, в большинстве случаев, характерно для 14-15 дюймовых моделей.

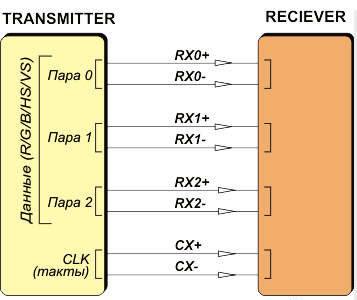

Интерфейс LVDS

Интерфейс LVDS на текущий момент времени является самым распространенным

интерфейсом из всех используемых в мониторах настольного типа и в

матрицах для ноутбуков. По сравнению с TMDS, интерфейсом LVDS

обеспечивается более высокая пропускная способность, что и привело к

тому, что LVDS, фактически, стал стандартом внешнего интерфейса для

современной LCD-панели.

LVDS (TIA/EIA-644) – Low Voltage Differential Signaling (низковольтная

дифференциальная передача сигналов) – это дифференциальный интерфейс для

скоростной передачи данных. Интерфейс разработан фирмой National

Semiconductor в 1994 году. Технология LVDS отражена в двух стандартах:

1. TIA/EIA (Telecommunications Industry Association/Electronic

Industries Association) - ANSI/TIA/EIA-644 (LVDS)

2. IEEE (Institute for Electrical and Electronics Engineering) - IEEE

1596.3

Кроме того, этот интерфейс часто используется под торговой маркой

FPD-Link TM. Вторым владельцем авторских прав на эту шину является

компания Texas Instruments, которая выпускает ее под фирменной торговой

маркой FlatLinkTM.

Интерфейс LVDS позже дорабатывался с целью увеличения пропускной

способности и повышения надежности передачи данных, а также он

выпускался другими разработчиками под разными торговыми марками, что

внесло некоторую неясность в классификацию интерфейсов и складывается

впечатление, что имеется множество различных шин. Так, например,

разновидностями и торговыми марками интерфейса LVDS являются:

- FPD-LinkTM;

- FlatLinkTM;

- PanelBusTM;

- LDI;

- OpenLDITM.

Интерфейс LVDS во многом схож с интерфейсом TMDS, особенно в плане

архитектуры и схемотехники. Здесь мы также имеем дело с дифференциальной

передачей данных в последовательном виде. А это означает, что интерфейс

LVDS подразумевает наличие трансмиттеров и ресиверов, осуществляющих

точно такое же преобразование данных, как и в TMDS (о чем достаточно

подробно рассказывалось в первой части статьи). Поэтому остановимся лишь

на особенностях, отличающих интерфейс LVDS от интерфейса TMDS.

LVDS способен передавать до 24 битов информации за один пиксельный такт,

что соответствует режиму True Color (16.7 млн. цветов). При этом

исходный поток параллельных данных (18 бит или 24 бита) конвертируется в

4 дифференциальные пары последовательных сигналов с умножением исходной

частоты в семь раз. Тактовая частота передается по отдельной

дифференциальной паре. Уровни рабочих сигналов составляют 345 мВ,

выходной ток передатчика имеет величину от 2.47 до 4.54 мА, а

стандартная нагрузка равна 100 Ом. Данный интерфейс позволяет обеспечить

надежную передачу данных с полосой пропускания свыше 455 МГц без

искажений на расстояние до нескольких метров.

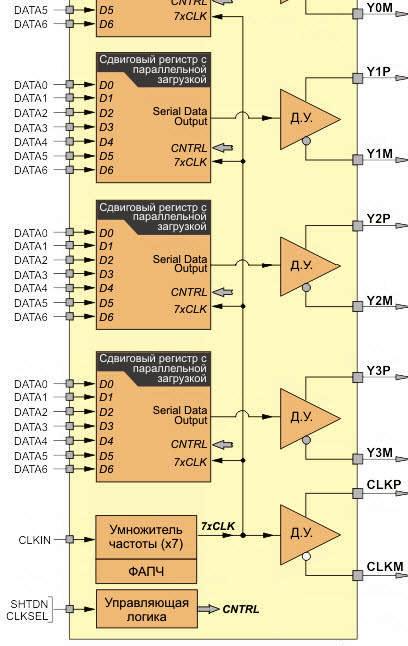

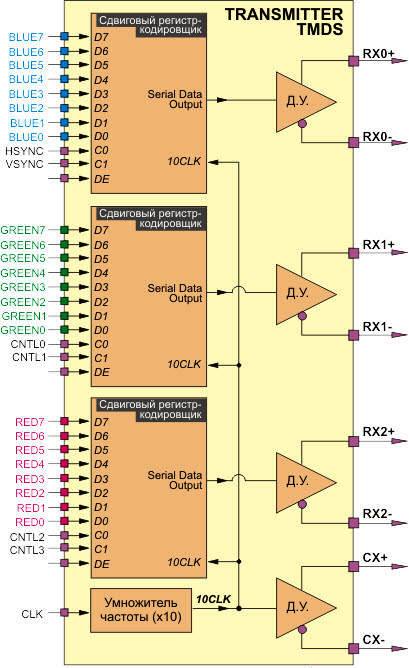

Трансмиттер LVDS состоит из четырех 7-разрядных сдвиговых регистров,

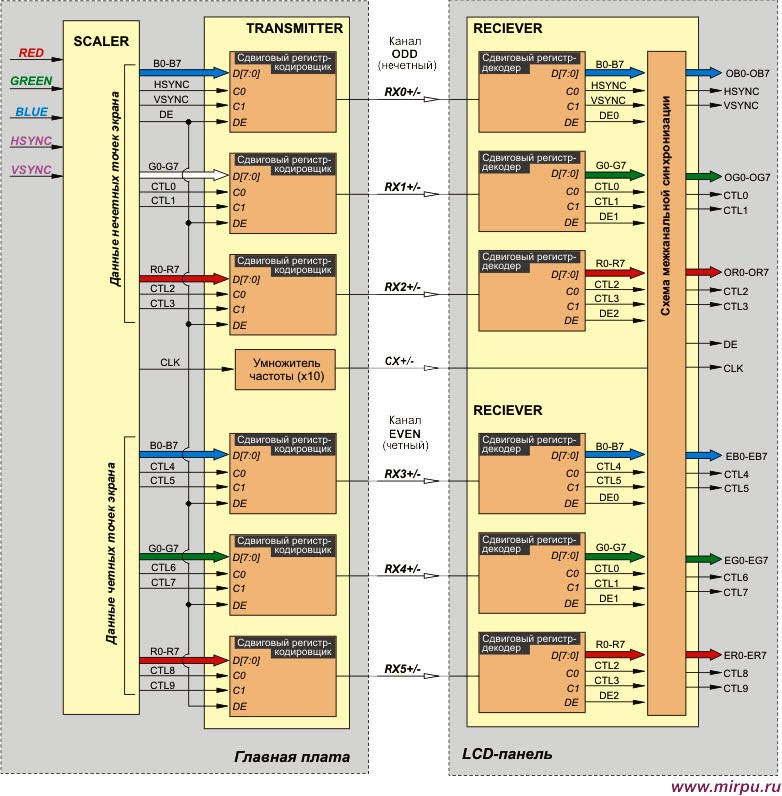

умножителя частоты и выходных дифференциальных усилителей (рис.18).

Рис.18

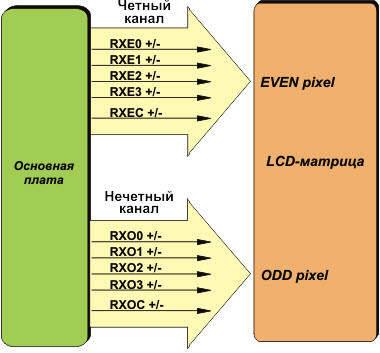

Достаточно часто в литературе, в

документации и на схемах можно встретить и несколько другое обозначение

сигналов интерфейса LVDS. Так, в частности, широко применяется такое

обозначение, как RX0+/-, RX1+/-, RX2+/-, RX3+/- и RXC+/-.

Входной сигнал CLK представляет

собой сигнал пиксельной частоты (Pixel Clock) и он определяет частоту

формирования сигналов R/G/B на входе трансмиттера. Умножитель частоты

умножает частоту CLK в 7 раз. Полученный тактовый сигнал (7xCLK)

используется для тактирования сдвиговых регистров, а также передается по

дифференциальным линиям CLKP/CLKM.

7-разрядный параллельный код

загружается в сдвиговые регистры трансмиттера по стробирующему сигналу,

вырабатываемому внутренней управляющей логикой трансмиттера. После

загрузки начинается поочередное «выталкивание» битов на соответствующую

дифференциальную линию, и этот процесс тактируется сигналом 7xCLK.

Таким образом, на каждой из

четырех дифференциальных линий данных (Y0P/YOM, Y1P/Y1M, Y2P/Y2M,

Y3P/Y3M ) формируется 7-разрядный последовательный код, передаваемый

синхронно с тактовыми сигналами на линии CLKP/CLKM.

Обратное преобразование

последовательного кода в параллельный осуществляется ресивером, входящим

в состав LCD-панели, а поэтому вполне естественно, что ресивер,

фактически, является зеркальным отражением трансмиттера.

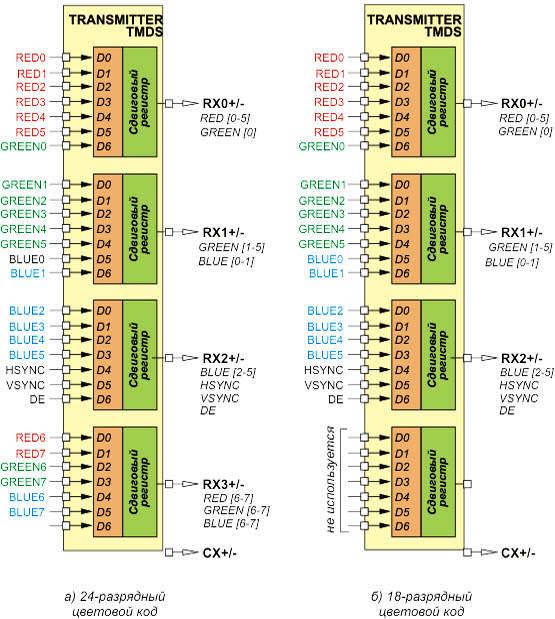

Интерфейс LVDS используется для

передачи как 18-разрябного цветового кода (3 цвета по 6 бит на каждый),

так и 24-разрядного цвета (3 базовых цвета по 8 бит). Но в отличие от

интерфейса TMDS, здесь каждому цвету не выделяется отдельная

дифференциальная пара, т.е. каждый дифференциальный канал LVDS

предназначен для передачи отдельных битов разных цветов. Кроме сигналов

цвета, на LCD-панель должны передаваться еще:

- сигнал строчной синхронизации (HSYNC);

- сигнал кадровой синхронизации (VSYNC);

- сигнал разрешения данных (DE).

Эти управляющие сигналы также

передаются по дифференциальным каналам, предназначенным для передачи

данных, т.е. по линиям YnP/YnM. Таким образом, существует два варианта

формата данных, передаваемых на LCD-матрицу.

Первый вариант соответствует

18-разрядному цветовому коду, и при этом на вход трансмиттера подается

21 разряд данных. Второй вариант – это 24-разрядный цветовой код, при

котором на входе трансмиттера должно быть 27 бит данных. Разница между

двумя этими вариантами, формально, небольшая и она отражена в табл.3.

Таблица 3.

|

18-разрядный цвет |

24-разрядный цвет |

|

R0-R5 |

R0-R7 |

|

G0-G5 |

G0-G7 |

|

B0-B5 |

B0-B7 |

|

HSYNC |

HSYNC |

|

VSYNC |

VSYNC |

|

DE |

DE |

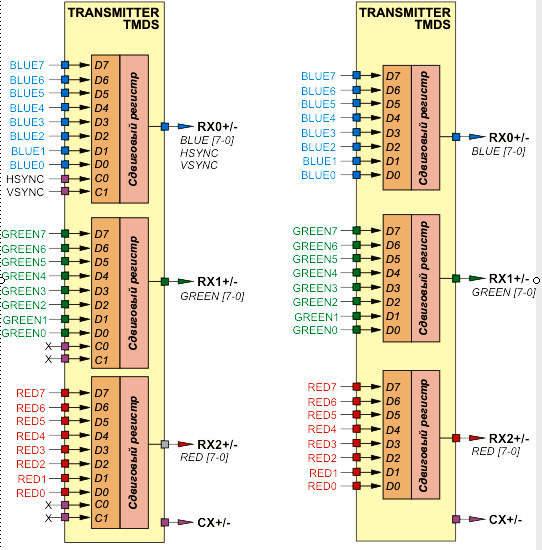

Общая

схема, поясняющая архитектуру интерфейса LVDS, представлена на рис.19. Рис.19

Рис.19

То, какие разряды цвета и служебные сигналы будут передаваться по дифференциальной линии, определяется сигналами, подаваемыми на вход соответствующего сдвигового регистра трансмиттера. При этом, конечно же, необходимо понимать, что ресивер, расположенный на LCD-панели, будет осуществлять преобразование в обратном порядке и на его выходе будет получен точно такой же формат данных. А это все означает, что вполне конкретная LCD-панель оказывается привязанной к конкретной управляющей плате монитора. Такая привязка LCD-панели к управляющей плате, конечно же, неудобна большинству производителей, т.к. отсутствует какая-либо унификация. Именно поэтому, де-факто, практически всеми производителями LCD-дисплеев и LCD-панелей использовался вполне определенный формат входных данных, позволявший к любой плате подключать любую панель. Этот формат данных стал основой стандарта, разработанного ассоциацией VESA, и на сегодняшний день можно говорить, что LVDS превратился в унифицированный интерфейс, в котором однозначно прописан протокол передачи, формат входных данных, соединительный разъем и цоколевка разъема. На этот стандарт мы и будем опираться, так как выпускаемые сейчас панели соответствуют именно ему, и встретить уникальные LVDS-интерфейсы практически невозможно.

Итак,

стандартный вариант распределения входных сигналов трансмиттера между

его сдвиговыми регистрами представлен на рис.20. Рис.20

Рис.20

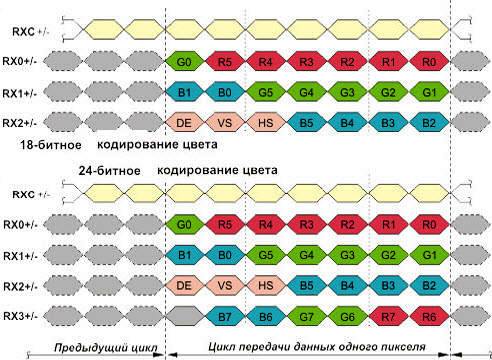

В результате, протокол передачи данных по дифференциальным каналам интерфейса LVDS выглядит так, как это показано на рис.21.

Рис.21

Как показывает внимательный анализ рис.20 и рис.21, интерфейс отличается высокой универсальностью, в результате чего, фактически, решен вопрос совместимости LCD-панелей и управляющих плат. Причем разработчик монитора имеет возможность практически не заботиться о согласовании разрядности цвета скалера и LCD-панели. Так, например, если разработчик решил применить более дешевую LCD-панель (с 18-битным кодированием цвета), то в интерфейсе не задействуется дифференциальный канал RX3, в результате чего старшие разряды цвета просто-напросто «обрубаются». А вот при разработке более дорогой модели монитора, в которой применяется LCD-панель с 24-битным кодированием, производитель использует ту же самую управляющую плату и даже не изменяет программный код ее микропроцессора, и просто подключает эту панель через полнофункциональный интерфейс – и все работает. Кроме того, производитель монитора в своем изделии может использовать любую матрицу любого производителя, лишь бы он была оснащена интерфейсом LVDS и имела бы соответствующий форм-фактор (который, к слову сказать, тоже стандартизируется). Конечно же, широкий модельный ряд мониторов не всегда получают таким примитивным образом, но и недооценивать этот метод тоже не стоит. Положительным моментом использования LVDS является еще и то, что все это дает широкие возможности сервисным специалистам при ремонте LCD-мониторов.

В

принципе, интерфейс LVDS может использоваться для передачи любых

цифровых данных, о чем говорит широкое применение LVDS в

телекоммуникационной отрасли. Однако, все-таки, наибольшее

распространение он получил именно как дисплейный интерфейс. Для

увеличения пропускной способности этого интерфейса, компания разработчик

(National Semiconductor) расширила интерфейс LVDS и удвоила количество

дифференциальных пар, используемых для передачи данных, т.е. теперь их

стало восемь (см. рис.22). Рис.22

Это расширение получило название LDI – LVDS Display Interface.

Кроме того, в спецификации LDI улучшен баланс линий по постоянному току

за счет введения избыточного кодирования, а стробирование производится

каждым фронтом такового сигнала (что позволяет вдвое повысить объем

передаваемых данных без увеличения тактовой частоты). LDI поддерживает

скорость передачи данных до 112 МГц. В документации данная спецификация

встречается также и под наименованием OpenLDITM, а у отечественных

специалистов отклик в душе нашел термин «двухканальный LVDS».

Рис.22

Это расширение получило название LDI – LVDS Display Interface.

Кроме того, в спецификации LDI улучшен баланс линий по постоянному току

за счет введения избыточного кодирования, а стробирование производится

каждым фронтом такового сигнала (что позволяет вдвое повысить объем

передаваемых данных без увеличения тактовой частоты). LDI поддерживает

скорость передачи данных до 112 МГц. В документации данная спецификация

встречается также и под наименованием OpenLDITM, а у отечественных

специалистов отклик в душе нашел термин «двухканальный LVDS».

Интересно отметить, что в интерфейсе LVDS (LDI) имеется 8

дифференциальных пар, предназначенных для передачи данных, и две

дифференциальные пары тактовых сигналов, т.е. в LDI имеется два,

практически, независимых полнофункциональных канала, передача данных в

каждом из которых тактируется собственным тактовым сигналом. Напомним,

что в двухканальном TMDS оба канала передачи данных тактируются единым

тактовым сигналом.

Естественно, что наличие двух каналов позволяет вдвое увеличить

пропускную способность интерфейса, так как за один пиксельный такт можно

предать информацию о двух пикселях. При этом один канал предназначен для

передачи четных точек экрана (канал Even), а второй – для нечетных точек

экрана (канал Odd).

Использование одноканального или двухканального LVDS определяется такими

характеристиками LCD-панели и монитора, как:

- размер экрана;

- разрешающая способность;

- частота кадровой развертки, т.е. определяется режимом работы.

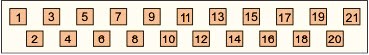

Разъем интерфейса LVDS на сегодняшний день можно считать стандартным,

т.е. количество контактов разъема и порядок распределения сигналов по

контактам является одинаковым для всех LCD-панелей любого производителя.

Единственное отличие разъемов может заключаться в их конструктивном

исполнении:

- разъем для плоского ленточного кабеля или традиционный разъем для

обычных соединительных проводов;

- наличие или отсутствие экрана;

- наличие или отсутствие дополнительных заземляющих контактов на краях

разъема;

- разъемы с разным шагом между контактами и т.п.

Стандартный разъем LVDS считается 30-контактным, хотя по его бокам могут

присутствовать еще два или четыре контакта, выполняющих «заземляющую»

функцию. Эти контакты в стандартном варианте не нумеруются, а

обозначаются как «Frame» и соединены со схемной «землей». Однако иногда

на схемах вы можете столкнуться с тем, что разъем LVDS обозначен, как

32-контактный. В этом случае следует помнить, что крайние контакты (1 и

32), как раз, и являются контактами «Frame», без учета которых интерфейс

сразу же превращается в стандартный 30-контактный разъем. Порядок

распределения сигналов интерфейса LVDS по контактам соединительного

разъема и их традиционное обозначение представлены в

табл.4.30-контактный разъем является полнофункциональным и предназначен

для двухканального LVDS. В LCD-панелях с небольшим размером экрана

(15-дюймов), чаще всего, используется одноканальный LVDS, т.к. его

пропускной способности вполне достаточно. В этом случае задействуется та

часть интерфейса, которая соответствует нечетному каналу LVDS, при этом

линии четного канала могут вообще отсутствовать.

Таблица 4.

|

№ |

Обознач. |

Описание |

|

Frame |

VSS |

Рама, каркас разъема (соединен с землей) |

|

1 |

RXO0- |

«-» для дифф. пары №0 нечетного канала |

|

2 |

RXO0+ |

«+» для дифф. пары №0 нечетного канала |

|

3 |

RXO1- |

«-» для дифф. пары №1 нечетного канала |

|

4 |

RXO1+ |

«+» для дифф. пары №1 нечетного канала |

|

5 |

RXO2- |

«-» для дифф. пары №2 нечетного канала |

|

6 |

RXO2+ |

«+» для дифф. пары №2 нечетного канала |

|

7 |

VSS |

Земля |

|

8 |

RXOC- |

«-» для дифф. пары сигнала CLK нечетного канала |

|

9 |

RXOC+ |

«+» для дифф. пары сигнала CLK нечетного канала |

|

10 |

RXO3- |

«-» для дифф. пары №3 нечетного канала |

|

11 |

RXO3+ |

«+» для дифф. пары №3 нечетного канала |

|

12 |

RXE0- |

«-» для дифф. пары №0 четного канала |

|

13 |

RXE0+ |

«+» для дифф. пары №0 четного канала |

|

14 |

VSS |

Земля |

|

15 |

RXE1- |

«-» для дифф. пары №1 четного канала |

|

16 |

RXE1+ |

«+» для дифф. пары №1 четного канала |

|

17 |

VSS |

Земля |

|

18 |

RXE2- |

«-» для дифф. пары №2 четного канала |

|

19 |

RXE2+ |

«+» для дифф. пары №2 четного канала |

|

20 |

RXEC- |

«-» для дифф. пары сигнала CLK четного канала |

|

21 |

RXEC+ |

«+» для дифф. пары сигнала CLK четного канала |

|

22 |

RXE3- |

«-» для дифф. пары №3 четного канала |

|

23 |

RXE3+ |

«+» для дифф. пары №3 четного канала |

|

24 |

VSS |

Земля |

|

25 |

VSS |

Земля |

|

26 |

NC (DE/ID) |

Не используется. Некоторые производители данный контакт используют в качестве сигнала разрешения матрицы или сигнала идентификации. Допускается и другое использование этого контакта. |

|

27 |

VSS |

Земля |

|

28 |

VCC |

Напряжение питания (+12V/+5V/+3.3V) |

|

29 |

VCC |

Напряжение питания (+12V/+5V/+3.3V) |

|

30 |

VCC |

Напряжение питания (+12V/+5V/+3.3V) |

|

Frame |

VSS |

Рама, каркас разъема (соединен с землей) |

Через интерфейс LVDS подается также и питающее напряжение для элементов

LCD-матрицы. Это напряжение, обозначаемое в табл.4 как VCC, может

представлять собой напряжение одного из трех номиналов:

- +3.3 V (обычно для 15-дюймовых матриц);

- +5V (для 15-дюймовых и 17-дюймовых матриц);

- +12V (обычно для 19-дюймовых матриц и больше).

Итак, интерфейс LVDS обеспечивает наилучшую из всех интерфейсов

универсальность соединения LCD-панели с главной платой монитора. Так же

как и в случае использования TMDS, на главной плате монитора должен

находиться LVDS-трансмиттер, а в состав LCD-панели должен входить

LVDS-ресивер. И трансмиттер и ресивер могут представлять собой как

отдельные микросхемы (что на сегодняшний день является достаточно редким

явлением), так и могут входить в состав скалера и TCON соответственно.

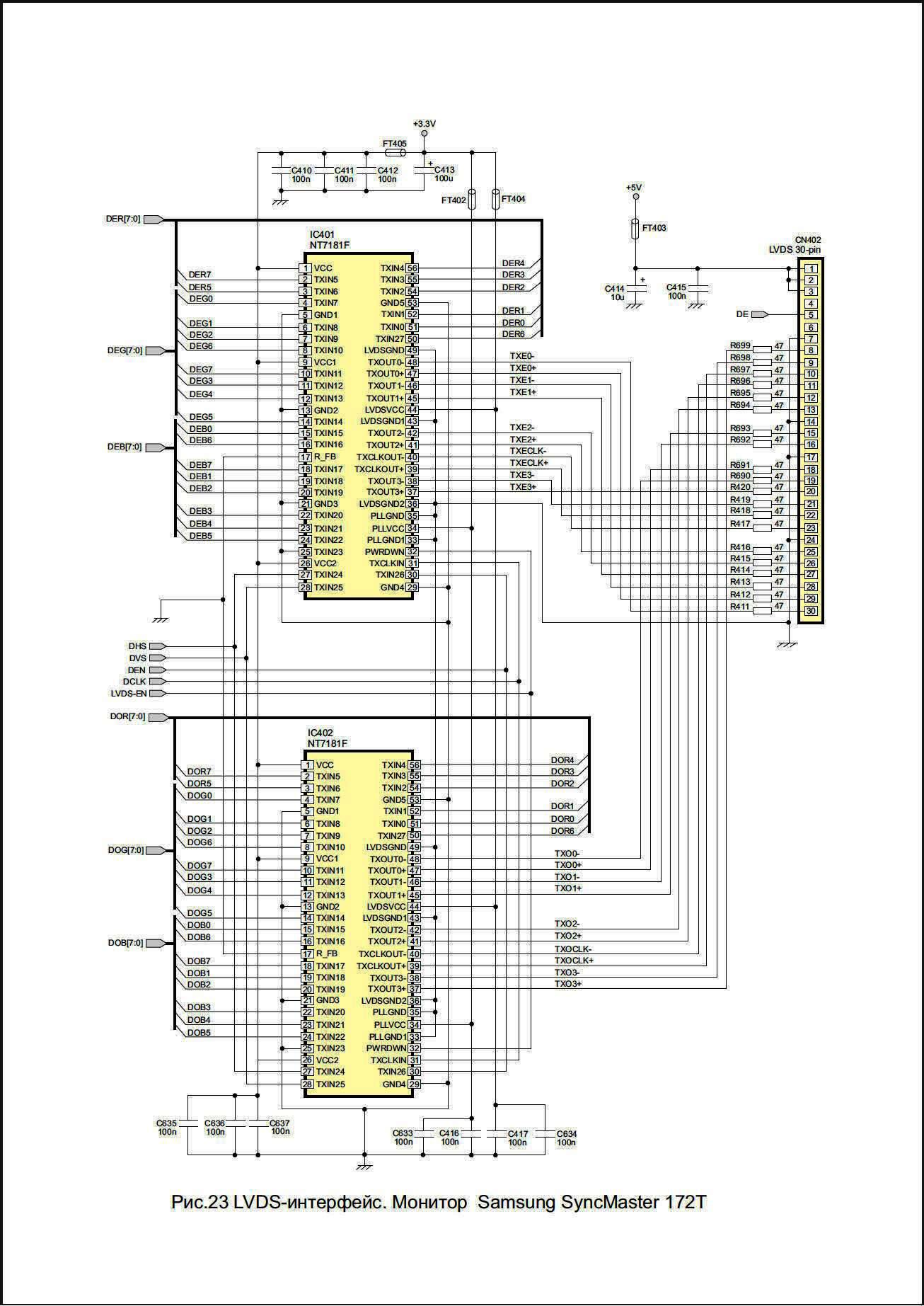

Если трансмиттер реализован в виде отдельной микросхемы, то необходимо

учесть что каждая такая микросхема представляет собой функционально

законченное устройство, обеспечивающее преобразование и передачу данных

одного канала. Естественно, что в этом случае для организации

двухканального LVDS, придется использовать две одинаковых микросхемы

трансмиттера. И здесь вполне понятно, что одна микросхема трансмиттера

предсталяет собой четный канал данных, а вторая – нечетный. Пример

подобного интерфейса представлен на рис.23, где изображен интерфейс LVDS

монитора Samsung SyncMaster 172T. В этом мониторе в качестве

трансмиттеров LVDS используются микросхемы NT7181F. На схеме следует

обратить внимание, что 30-контактный разъем LVDS (CN402) является

зеркальным отражением той цоколевки, которая была представлена в табл.4

(т.е. в таблице 4 мы представили распределение сигналов по контактам

разъема на стороне LCD-матрицы).

Рис.23

Следует упомянуть, что иногда, все-таки, можно встретить и нестандартные разъемы интерфейса LVDS. Особенно это касается мониторов уже устаревших моделей. Широкое распространение получил 20-контактный разъем, который часто встречается в мониторах LG, Philips, Samsung и других брэндов, использующих матрицы этих производителей. 20-контактный разъем использовался как для одноканального LVDS , так и для двухканального LVDS. При этом нужно отметить отсутствие каких-либо стандартов на распределение сигналов по контактам этих разъемов. Так, в частности, компанией Samsung в 15-дюймовых панелях достаточно широко использовался, так называемый, 20-контатный разъем LVDS, хотя в реальности на этом разъеме присутствует 22 контакта. Этот разъем предназначался для одноканального LVDS, и распределение сигналов на нем приводится в табл.5.

Таблица 5.

|

№ |

Обознач. |

Описание |

|

1 |

VCC |

Напряжение питания (+3.3V) |

|

2 |

VCC |

Напряжение питания (+3.3V) |

|

3 |

VSS |

Земля |

|

4 |

VSS |

Земля |

|

5 |

RX0- |

«-» для дифф. пары №0 |

|

6 |

RX0+ |

«+» для дифф. пары №0 |

|

7 |

VSS |

Земля |

|

8 |

RX1- |

«-» для дифф. пары №1 |

|

9 |

RX1+ |

«+» для дифф. пары №1 |

|

10 |

VSS |

Земля |

|

11 |

RX2- |

«-» для дифф. пары №2 |

|

12 |

RX2+ |

«+» для дифф. пары №2 |

|

13 |

VSS |

Земля |

|

14 |

RXC- |

«-» для дифф. пары сигнала CLK |

|

15 |

RXC+ |

«+» для дифф. пары сигнала CLK |

|

16 |

VSS |

Земля |

|

17 |

RX3- |

«-» для дифф. пары №3 |

|

18 |

RX3+ |

«+» для дифф. пары №3 |

|

19 |

VSS |

Земля |

|

20 |

VCC |

Напряжение питания (+3.3V) |

|

21 |

Frame |

Земля |

|

22 |

Frame |

Земля |

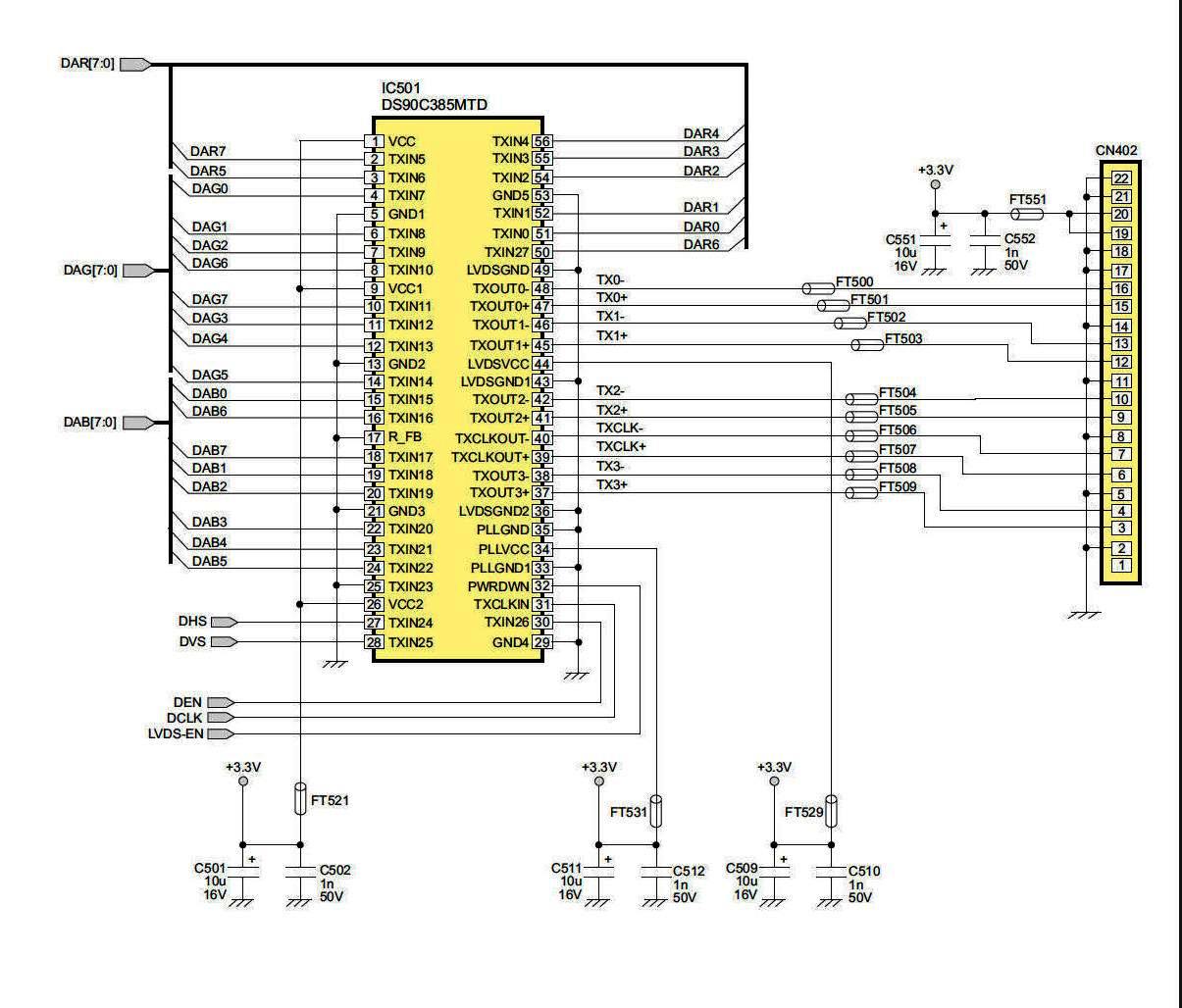

Пример одноканального интерфейса LVDS с 22-контаткным разъемом и отдельной микросхемой трансмиттера представлен на рис.24.

Рис.24

Чтобы просмотреть рис.24 подробнее, нажмите на ссылку.

Компаниями Philips и LG тоже применялся 22-контактный разъем, но в отличие от Samsung, этот разъем имел совершенно другую цоколевку (см. табл.6).

Таблица 6.

|

№ |

Обознач. |

Описание |

|

1 |

Frame |

Земля |

|

2 |

Frame |

Земля |

|

3 |

NC |

Не используется |

|

4 |

FR0M |

«-» для дифф. пары №0 |

|

5 |

VSS |

Земля |

|

6 |

FR0P |

«+» для дифф. пары №0 |

|

7 |

VCC |

Напряжение питания (+5V) |

|

8 |

FR1M |

«-» для дифф. пары №1 |

|

9 |

VSS |

Земля |

|

10 |

FR1P |

«+» для дифф. пары №1 |

|

11 |

VCC |

Напряжение питания (+5V) |

|

12 |

FR2M |

«-» для дифф. пары №2 |

|

13 |

VSS |

Земля |

|

14 |

FR2P |

«+» для дифф. пары №2 |

|

15 |

VSS |

Земля |

|

16 |

FCLKM |

«-» для дифф. пары сигнала CLK |

|

17 |

VSS |

Земля |

|

18 |

FCLKP |

«+» для дифф. пары сигнала CLK |

|

19 |

VSS |

Земля |

|

20 |

FR3M |

«-» для дифф. пары №3 |

|

21 |

VSS |

Земля |

|

22 |

FR3P |

«+» для дифф. пары №3 |

Кроме того, в относительно современных 15-дюймовых мониторах LG, например в LG Flatron L1510P, использовался реальный 20-контактный разъем для передачи данных одноканального LVDS. Распределение сигналов по контактам данного разъема приводится в табл.7.

Таблица 7.

|

№ |

Обознач. |

Описание |

|

1 |

NC |

Не используется |

|

2 |

VSS |

Земля |

|

3 |

Y3P |

«+» для дифф. пары №3 |

|

4 |

Y3M |

«-» для дифф. пары №3 |

|

5 |

VSS |

Земля |

|

6 |

CLKP |

«+» для дифф. пары сигнала CLK |

|

7 |

CLKM |

«-» для дифф. пары сигнала CLK |

|

8 |

VSS |

Земля |

|

9 |

Y2P |

«+» для дифф. пары №2 |

|

10 |

Y2M |

«-» для дифф. пары №2 |

|

11 |

VSS |

Земля |

|

12 |

Y1P |

«+» для дифф. пары №1 |

|

13 |

Y1M |

«-» для дифф. пары №1 |

|

14 |

VSS |

Земля |

|

15 |

Y0P |

«+» для дифф. пары №0 |

|

16 |

Y0M |

«-» для дифф. пары №0 |

|

17 |

VSS |

Земля |

|

18 |

VSS |

Земля |

|

19 |

VCC |

Напряжение питания (+3.3V/+5V) |

|

20 |

VCC |

Напряжение питания (+3.3V/+5V) |

Другой вариант 20-контактного разъема интерфейса LVDS применялся фирмами Philips и LG в 15/17 и 18-дюймовых матрицах, в которых передача данных осуществлялась с использованием 2-канального LVDS. При этом, 20-контактный разъем предназначался исключительно для передачи данных и на нем отсутствуют контакты питания и земли. Питающее напряжение и сигнальная земля LCD-матрицы в данном случае выведены на другой разъем, обычно 5-контаткный. Распределение сигналов двухканального LVDS по контактам 20-пинового разъема в мониторах Philips и LG, представлено в табл.8.

Таблица 8.

|

№ |

Обознач. |

Описание |

|

1 |

FR3P |

«+» для дифф. пары №3 (нечетный канал) |

|

2 |

FR3M |

«-» для дифф. пары №3 (нечетный канал) |

|

3 |

FCLKP |

«+» для дифф. пары сигнала CLK (нечетный канал) |

|

4 |

FCLKM |

«-» для дифф. пары сигнала CLK (нечетный канал) |

|

5 |

FR2P |

«+» для дифф. пары №2 (нечетный канал) |

|

6 |

FR2M |

«-» для дифф. пары №2 (нечетный канал) |

|

7 |

FR1P |

«+» для дифф. пары №1 (нечетный канал) |

|

8 |

FR1M |

«-» для дифф. пары №1 (нечетный канал) |

|

9 |

FR0P |

«+» для дифф. пары №0 (нечетный канал) |

|

10 |

FR0M |

«-» для дифф. пары №0 (нечетный канал) |

|

11 |

SR3P |

«+» для дифф. пары №3 (четный канал) |

|

12 |

SR3M |

«-» для дифф. пары №3 (четный канал) |

|

13 |

SCLKP |

«+» для дифф. пары сигнала CLK (четный канал) |

|

14 |

SCLKM |

«-» для дифф. пары сигнала CLK (четный канал) |

|

15 |

SR2P |

«+» для дифф. пары №2 (четный канал) |

|

16 |

SR2M |

«-» для дифф. пары №2 (четный канал) |

|

17 |

SR1P |

«+» для дифф. пары №1 (четный канал) |

|

18 |

SR1M |

«-» для дифф. пары №1 (четный канал) |

|

19 |

SR0P |

«+» для дифф. пары №0 (четный канал) |

|

20 |

SR0M |

«-» для дифф. пары №0 (четный канал) |

Как видно из всего этого, при применении на LCD-матрице 20-контактного разъема говорить о совместимости панелей различных производителей говорить не приходится (именно эту проблему и пытались решить введением стандартного 30-пинового разъема).

Еще раз обращаем внимание на то, что цоколевка разъемов во всех таблицах представлена со стороны LCD-матрицы. Это означает, что на основной плате монитора она имеет обратный порядок.